IBM z10は、IBMのIBM System z10 メインフレーム用のマイクロプロセッサで、2008年2月にリリースされた。開発中には "z6" と呼ばれていた。

概要

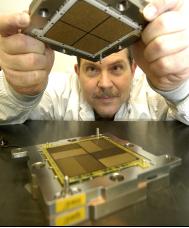

IBM z10 プロセッサは、CISCのz/Architectureの実装であり、4コアである。各コアは 64KB のL1 命令キャッシュと、128KB の L1 データキャッシュ、3MB の L2 キャッシュ(IBMは L1.5 キャッシュと呼ぶ)、そして 24MB の共用 L3 キャッシュ(IBMは L2 キャッシュと呼ぶ)を持つ。

IBMの 65nm SOI 半導体製造プロセス(CMOS 11S)で製造され、21.7×20.0 mmのチップサイズ上に993 百万トランジスタが搭載されている。サポートされているクロックは 4.4 GHz (前身の IBM System z9 の2倍以上) で、15 FO4 サイクルを持つ。

各 z10 チップは2つの 48GB/s SMPハブポート、4つの 13GB/s メモリポート、2つの 17GB/s I/Oポートを持ち、8765 とコンタクトする。

z10プロセッサは、POWER6プロセッサと多くの設計上の特徴を共有して開発された。半導体製造技術、ロジック設計、実行ユニット、浮動小数点数ユニット、バステクノロジー、パイプラインの設計スタイルなどである。

しかし、z10プロセッサは他の面では全く異なる。キャッシュの階層やキャッシュコヒーレンシ、SMPの技術やプロトコル、チップの構成などである。命令セットアーキテクチャ(ISA)は非常に異なり、z10 独自の 894 の命令があり、その 75% は完全にハードウェアとして実装されている。z/Architecture は CISCのアーキテクチャであり、1960年代のSystem/360からの互換性を保っている。

前身のIBM System z9 EC プロセッサからの追加は以下である。

- コードをより効率的に実行するための 50以上の新しい命令

- ソフトウェア/ハードウェア キャッシュの最適化

- 1MB ページフレームのサポート

- 10進数の浮動小数点数が完全にハードウェアに実装された

エラー検知とリカバリーが強化され、L2、L3 キャッシュとバッファーに ECC (error-correcting code)や拡張されたパリティチェックが備わり、チップ全体で 20,000 のエラーチェッカーが備わった。大半のハードウェアエラーを検知しリトライするために、プロセッサの状態はバッファーされる。

参照

関連項目

- マイクロプロセッサ

- CISC

- System z

- z/OS

- POWER

- メインフレーム

外部リンク

- Is IBM's New Z10 a Big Deal?

- Redbook Draft: IBM System z10 Enterprise Class Technical Introduction

- IBM System z10 Enterprise Class – Datasheet

- IBM Readies Quad-Core z6 Chip for Mainframe Iron – IT Jungle

- IBM Journal Of Research And Development Issue On System Z10